Arithmetic Circuits – Basic Building Blocks

- Mengetahui dan memahami aplikasi rangkaian full subtractor dan controlled inverter

- Mampu menjelaskan prinsip serta cara kerja dari rangkaian full subtractor dan controlled inverter

- Mengetahui jenisjenis rangkaian aritmatika

- Alat

- Bahan

Gerbang XOR merupakan gerbang logika yang outputnya akan bernilai benar atau “1” jika nilai input-inputnya berbeda dan bernilai salah atau “0” jika nilainya sama.

3) Gerbang OR

Gerbang logika OR merupakan gerbang logika yang outpunya (Y) akan bernilai benar atau “1” jika terdapat salah satu input yang bernilai benar “1”.

4) Gerbang NOT

Gerbang logika NOT merupakan gerbang yang berfungsi sebagai pembalik keadaan logika. Jika input “0” maka outputnya bernilai “1” dan begtu sebaliknya.

5) Gerbang AND

Gerbang logika AND merupakan gerbang logika yang outputnya (Y) hanya akan bernilai benar atau “1” jika semua inputnya (A&B) bernilai benar atau “1”.

Aplikasi pengurangan penuh atau Full subtractor adalah salah satu rangkaian logika kombinasional yang paling banyak digunakan dan esensial. Ini adalah perangkat elektronik dasar, yang digunakan untuk melakukan pengurangan dua bilangan biner.

Ekspresi Boolean untuk dua variabel output diberikan oleh persamaan

Perancangan ini dapat dilakukan dengan dua setengah subtractor, yang melibatkan tiga input seperti minuend, subtrahend, dan borrow, bit pinjam antar input diperoleh dari pengurangan dua digit biner dan dikurangkan dari pasangan orde tinggi berikutnya dari bit, output sebagai perbedaan dan meminjam.

e.) Controlled Inverter

Inverter terkontrol diperlukan ketika penambah akan digunakan sebagai pengurang. Seperti yang diuraikan sebelumnya, pengurangan tidak lain adalah penambahan komplemen 2 dari pengurangan ke minuend. Dengan demikian, Langkah pertama menuju implementasi praktis dari sebuah subtractor adalah menentukan komplemen 2 dari pengurang. Dan untuk ini, pertama-tama kita perlu menemukan pelengkap 1. Inverter terkontrol digunakan untuk menemukan pelengkap 1. Inverter terkontrol satu bit tidak lain adalah gerbang EX-OR dua input dengan salah satu input diperlakukan sebagai input kontrol,

a.Prosedur percobaan

- Siapkan segala komponen yang di butuhkan

- Susun rangkaian sesuai panduan

- Apabila tidak terjadi eror, maka rangkaian selesai dibuat.

b. Hardware

c. Rangkaian simulasi

- Foto Rangkaian

- Gambar Rangkaian Simulasi Half-AdderPrinsip KerjaLogika A masuk ke input A gerbang logika XOR dan AND. Lalu Logika B masuk ke input B gerbang logika XOR dan AND. Gerbang Logika XOR akan mengeluarkan output yang akan menjadi nilai penjumlahan atau nilai S. Output gerbang logika AND akan menjadi nilai pembawa atau C.Gambar Rangkaian Simulasi Half-adder dengan gerbang NANDPrinsip KerjaRangkaian di atas merupakan rangkaian Half-Adder dengan gerbang logika AND. Logika A (Logicstate atas) akan masuk ke kaki A gerbang logika U1A dan kaki A gerbang logka U1B. Logika B (logicstate bawah) akan masuk ke kaku B gerbang logika U1A dan kaki B gerbang Logika U1C. Kemudian U1A akan mengeluarkan logika yang kemudian logika tersebut masuk ke kaki B U1B, kaki A U1C serta kaki A dan B gerbang logika U2A. Output Dari U1B menjadi input kaki A U1 D dan output U1C menjadi input kaki B U1D. Output dari U1D akan menjadi nilai S dan output U2 A menjadi nilai C.Gambar Rangkaian Simulasi Full-AdderLogika Cin masuk ke input A Gerbang Logika XOR U3 dan AND U6. Logika A masuk ke input A gerbang logika XOR U4 dan AND U5. Lalu Logika B masuk ke input B gerbang logika XOR U4 dan AND U5. Output gerbang logika XOR U4 akan masuk ke input B Gerbang logika XOR U3 dan AND U6. Output XOR U3 akan menjadi nilai penjumlahan atau S. Output gerbang logika AND U6 akan masuk ke input A gerbang logika OR U7. Nilai output dari gerbang logika AND U5 akan menjadi input B dari gerbang logika OR U7. Output gerbang logika OR U7 akan menjadi nilai pembawa atau C.Gambar Rangkaian Simulasi Full-adder 2Prinsip KerjaRangkaian Kiri. logika A' akan masuk ke kaki A U3 dan kaki A U4, Logika B' akan masuk ke kaki B U3 dan kaki B U5, logika Cin akan masuk ke kaki C U3 dan kaki C U6, logika A akan masuk ke kaki U5 dan U6, Logika B akan masuk ke kaki B U4 dan kaki B U6, dan Logiika Cin' akan masuk ke kaki C U4 dan kaki C U5. Kemudian output dari U3 akan masuk ke kaki A U7, output U4 akan masuk ke kaki B gerbang logika U7, Output U5 akan masuk ke kaki C U7, dan output U6 akan masuk ke kaki D U7. Kemudian Output dari U7 merupakan nilai S.Rangkaian kanan. Logika A akan masuk ke kaki A U8 dan U10 lalu logika B akan masuk ke kaki U8 dan kaki A U9 dan logika Cin akan masuk ke kaki B U9 dan U10. Kemudian output dari U8 akan masuk ke kaki U11, output U9 akan asuk ke kaki B U11 dan output U10 akan masuk ke kaki C U11. Lalu output U11 merupakan nilai Cout.Gambar Rangkaian Simulasi Half-SubtractorPrinsip Kerja

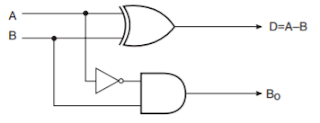

Logika A masuk ke input A gerbang logika XOR dan ke inverter sehingga nilai logika A dibalik lalu masuk ke gerbang logika AND. Lalu Logika B masuk ke input B gerbang logika XOR dan AND. Gerbang Logika XOR akan mengeluarkan output yang akan menjadi nilai perbedaan atau nilai D. Output gerbang logika AND akan menjadi nilai peminjam atau B0.

- Prinsip Kerja

- Prinsip Kerja

- Example

- Problem

- Pilihan Ganda

Tidak ada komentar:

Posting Komentar